MUX4_to_1

4:1 멀티플렉서

s1s0신호에 따라서 y0~y3의 신호가 출려됨

module MUX4_to_1(

output wire OUT,

input wire I0, I1, I2, I3,

input wire S1, S0

);

wire s1n, s0n;

wire y0, y1, y2, y3;

not (s1n, S1);

not (s0n, S0);

and (y0, I0, s1n, s0n);

and (y1, I1, s1n, S0);

and (y2, I2, S1, s0n);

and (y3, I3, S1, S0);

or (OUT, y0, y1, y2, y3);

endmoduletb_mux

`timescale 10ns/1ps

module tb_mux;

reg IN0, IN1, IN2, IN3;

reg S0, S1;

wire OUTPUT;

MUX4_to_1 mymux(

.OUT (OUTPUT),

.I0 (IN0 ),

.I1 (IN1 ),

.I2 (IN2 ),

.I3 (IN3 ),

.S1 (S1 ),

.S0 (S0 )

);

initial begin

IN0 = 1'b0; IN1 = 1'b0; IN2 = 1'b1; IN3 = 1'b1;

S1 = 1'b0; S0 = 1'b0;

# 1 S1 = 1'b0; S0 = 1'b1;

# 1 S1 = 1'b1; S0 = 1'b0;

# 1 S1 = 1'b1; S0 = 1'b1;

#5

$finish;

end

endmodule

ha

module Half_Adder (

output wire SUM, CARRY,

input wire X,Y

);

and (CARRY, X, Y);

xor (SUM, X, Y);

endmoduletb_ha

`timescale 10ns/1ps

module tb_half_adder;

reg X, Y;

wire SUM, CARRY;

Half_Adder myha(SUM, CARRY, X, Y);

initial

begin

X=1'b0 ; Y = 1'b0;

#1 X=1'b0 ; Y = 1'b1;

#1 X=1'b1 ; Y = 1'b0;

#1 X=1'b1 ; Y = 1'b1;

#1 X=1'b0 ; Y = 1'b0;

#1 X=1'b0 ; Y = 1'b0;

end

endmodule

fa

module Full_Adder (

output wire SUM, CARRY_OUT,

input wire X,Y,CARRY_IN

);

wire sum1;

wire carry1, carry2;

// HA (SUM, CARRY, X, Y) ???

Half_Adder ha0 (sum1, carry1, X, Y);

Half_Adder ha1 (SUM, carry2, sum1, CARRY_IN);

or (CARRY_OUT, carry1, carry2);

endmoduletb_fa

`timescale 10ns/1ps

module tb_full_adder;

reg X,Y,CARRY_IN;

wire SUM, CARRY_OUT;

Full_Adder myfa (SUM, CARRY_OUT, X, Y, CARRY_IN);

initial begin

X = 1'b0; Y = 1'b0; CARRY_IN = 1'b0;

#1 X = 1'b0; Y = 1'b0; CARRY_IN = 1'b0;

#1 X = 1'b0; Y = 1'b1; CARRY_IN = 1'b1;

#1 X = 1'b1; Y = 1'b0; CARRY_IN = 1'b0;

#1 X = 1'b1; Y = 1'b1; CARRY_IN = 1'b0;

#1 X = 1'b1; Y = 1'b1; CARRY_IN = 1'b1;

#1 X = 1'b0; Y = 1'b1; CARRY_IN = 1'b1;

#1 X = 1'b0; Y = 1'b0; CARRY_IN = 1'b1;

#1 X = 1'b0; Y = 1'b0; CARRY_IN = 1'b0;

end

endmodule

fulladder ==ripple carry adder

module fulladder4b(

output wire [3:0] SUM,

output wire CARRY_OUT,

input wire [3:0] X,

input wire [3:0] Y,

input wire CARRY_IN

);

wire c1, c2, c3;

// Full_Adder ( output wire SUM, CARRY_OUT, input wire X,Y,CARRY_IN); // ãナ변수 순서 참고

Full_Adder fa0 (SUM[0], c1, X[0], Y[0], CARRY_IN);

Full_Adder fa1 (SUM[1], c2, X[1], Y[1], c1);

Full_Adder fa2 (SUM[2], c3, X[2], Y[2], c2);

Full_Adder fa3 (SUM[3], CARRY_OUT, X[3], Y[3], c3);

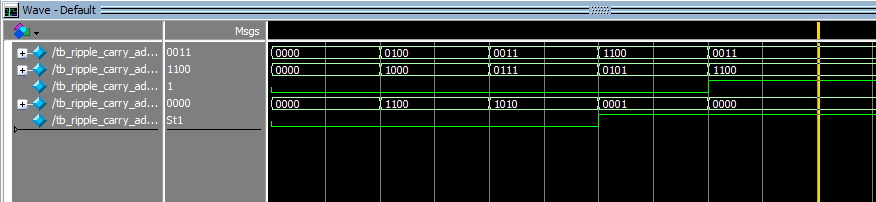

endmoduletb_ripple carry adder

`timescale 10ns/1ps

module tb_ripple_carry_adder;

reg [3:0] X;

reg [3:0] Y;

reg CARRY_IN;

wire [3:0] SUM;

wire CARRY_OUT;

fulladder4b fa4b (SUM, CARRY_OUT, X, Y, CARRY_IN);

initial begin

/*

X=4'b0000; Y=4'b0000; CARRY_IN = 1'b0;

#1 X=4'b0000; Y=4'b0001; CARRY_IN = 1'b0;

#1 X=4'b0000; Y=4'b0001; CARRY_IN = 1'b0;

#1 X=4'b1100; Y=4'b0011; CARRY_IN = 1'b0;

#1 X=4'b1100; Y=4'b0011; CARRY_IN = 1'b1;

#1 X=4'b1111; Y=4'b1111; CARRY_IN = 1'b1;*/

X=4'b0000; Y=4'b0000; CARRY_IN = 1'b0; // carry_in 초기화 중요

# 1 X=4'b0100; Y=4'b1000;

# 1 X=4'b0011; Y=4'b0111;

# 1 X=4'b1100; Y=4'b0101;

# 1 X=4'b0011; Y=4'b1100;

# 10;

end

endmodule

'FW 심화 과정 > [1] HDL, ARM프로세서설계' 카테고리의 다른 글

| 0623 실습 3-1~3-3 (0) | 2022.06.23 |

|---|---|

| 0622 실습 2-1~2-4 (0) | 2022.06.22 |

| 강의 영상 보는 곳 & modelsim 설치 (0) | 2022.06.21 |

| 0620 반도체 설계 방법 (0) | 2022.06.20 |

| 0620 Verilog Lexical (문법) (0) | 2022.06.20 |

| 동기 순차회로 vs 비동기 순차회로 (0) | 2022.04.23 |