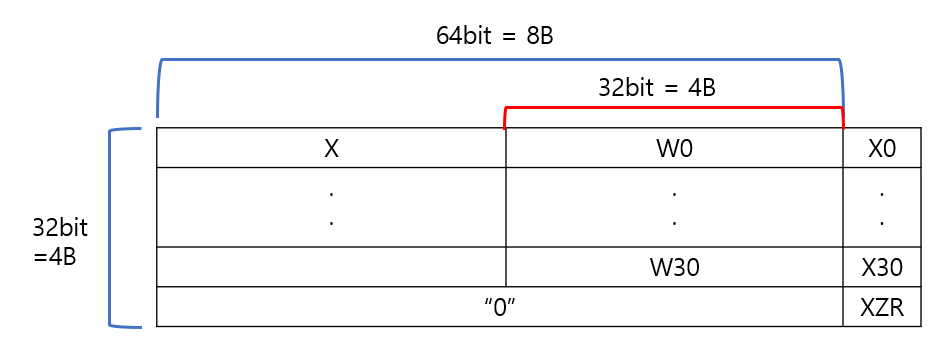

- 멀티플렉서 자체는 ALU의 Zero 출력과 현재 명령어가 분기라는 것을 나타내는 제어선을 AND하는 게이트에 의해 제어된다. - 멀티 플렉서는 서로 다른 근원지에서 나온 데이터가 같은 유닛으로 가는 경우를 위해서 필요하다 - PC에 들어갈 값은 두 덧셈기(PC+4, TA)중 하나이고, 레지스터 파일에 쓰일 데이터는 ALU나 데이터 메모리에서 나오며, ALU의 두번째 입력은 레지스터나 명령어의 수치필드에서 나온다(18비트 명령어 필드). - 데이터 메모리는 LOAD일때는 읽기, SAVE일때는 쓰기 레지스터 파일은 LOAD나 산술/논리 일대만 쓰기. - 레지스터 피연산자 세 개이므로 매 명령어 마다 레지스터파일에서 두 데이터를 읽고 데이터 워드 하나를 써야 함. - 따라서, 레지스터번호용 세 개, 데이터..